#### DECLARATION

I, Kaori HIRAKI, of KOKUBUN International Patents & Trademarks of NBF Ikebukuro City Building, 17-8, Higashi-Ikebukuro 1-chome, Toshima-ku, Tokyo 170-0013 JAPAN, hereby declare that I am well acquainted with both the Japanese and English languages, that I made an English translation attached hereto, and that to the best of my knowledge and belief the translation is a true and correct reproduction of the original documents filed with the Japanese Patent Office in respect of Japanese Patent Application No. 2002-355933 on December 6, 2002.

Signed this 25th day of October, 2005

H. Wiraki

Kaori HIRAKI

BEST AVAILABLE COPY

[Name of document] APPLICATION FOR PATENT [Reference number] 0200175 [Date] December 6, 2002 [Designation] Commissioner, Patent Office [IPC] H01L 21/00 [Title of the invention] SEMICONDUCTOR MEMORY DEVICE AND METHOD OF FABRICATING THE SAME [Number of claims] 10 [Inventor] [Address] c/o FUJITU AMD SEMICONDUCTOR LIMITED, 6, Kogyodanchi, Monden-machi, Aizuwakamatsu-shi, Fukushima [Name] Hideo TAKAGI [Inventor] c/o FUJITU AMD SEMICONDUCTOR LIMITED, 6, [Address] Kogyodanchi, Monden-machi, Aizuwakamatsu-shi, Fukushima [Name] Takayuki ENDA [Inventor] c/o FUJITU AMD SEMICONDUCTOR LIMITED, 6, [Address] Kogyodanchi, Monden-machi, Aizuwakamatsu-shi, Fukushima [Name] Miyuki UMETSU [Inventor] C/O FUJITU AND SEMICONDUCTOR LIMITED, 6, [Address] Kogyodanchi, Monden-machi, Aizuwakamatsu-shi, Fukushima [Name] Tsukasa WAKAMATSU [Applicant for patent] [Identification number] 596180124

[Name] FUJITSU AMD SEMICONDUCTOR LIMITED

[Agent]

| [Identification number]   | 100090273     |        |

|---------------------------|---------------|--------|

| [Patent Attorney]         |               |        |

| [Name]                    | Takayoshi KOF | UBUN   |

| [Telephone number]        | 03-3590-8901  |        |

| [Official fees]           |               |        |

| [Deposit number]          | 035493        |        |

| [Amount]                  | 21,000        | . •    |

| [Attached documents]      |               |        |

| [Document]                | Specification | 1      |

| [Document]                | Drawing       | 1      |

| [Document]                | Abstract      | 1      |

| [General power of attorne | y number]     | 011517 |

| [Necessity of proof]      | Necessary     |        |

[NAME OF DOCUMENT] SPECIFICATION [TITLE OF THE INVENTION] SEMICONDUCTOR MEMORY DEVICE AND METHOD OF FABRICATING THE SAME [WHAT IS CLAIMED IS:]

[CLAIM 1]

A method of fabricating a semiconductor memory device comprising the steps of:

forming a charge storage film for storing electric charge; and

erasing electric charge stored in said charge storage film by subjecting said charge storage film to hydrogen plasma treatment after the formation thereof.

[CLAIM 2]

The method of fabricating a semiconductor memory device according to Claim 1, wherein said plasma treatment is carried out over a duration of time of 40 seconds to 90 seconds.

[CLAIM 3]

The method of fabricating a semiconductor memory device according to Claims 1 or 2, further comprising, after the formation of said charge storage film, a step of forming a contact hole through which a wiring connection is to be established, and then subjecting said film to said hydrogen plasma treatment through said contact hole.

[CLAIM 4]

The method of fabricating a semiconductor memory device according to Claim 3, wherein said plasma treatment is carried out before, during, or after a barrier metal is formed along the inner wall of said contact hole.

[CLAIM 5]

The method of fabricating a semiconductor memory device according to any one of Claims 1 to 4, wherein said plasma treatment is carried out at 350°C to 450°C.

[CLAIM 6]

A method of fabricating a semiconductor memory device comprising the steps of:

forming a charge storage film for storing electric charge; and

erasing electric charge stored in said charge storage film by subjecting said charge storage film to hydrogen annealing after the formation thereof.

[CLAIM 7]

The method of fabricating a semiconductor memory device according to Claim 6, further comprising, after the formation of said charge storage film, a step of forming a contact hole through which a wiring connection is to be established and then subjecting said film to said hydrogen annealing treatment through said contact hole.

[CLAIM 8]

The method of fabricating a semiconductor memory device according to Claims 6 or 7, wherein said annealing is carried out at 400°C or above.

[CLAIM 9]

The method of fabricating a semiconductor memory device according to any one of Claims 1 to 8, wherein said charge storage film is any one of a nitride film, a double-layered film comprising an oxide film and a nitride film, and a three-layered film comprising an oxide film, a nitride film and an oxide film.

[CLAIM 10]

A semiconductor memory device having a charge storage film for storing electric charge, said semiconductor memory device comprising:

first contact hole used for wiring connection, and;

second contact hole not used for wiring connection but used for facilitating diffusion of hydrogen radicals or hydrogen molecules into said charge storage film.

[DETAILED DESCRIPTION OF THE INVENTION]

[0001]

[FIELD OF THE INDUSTRIAL AVAILABILITY]

The present invention relates to a semiconductor memory device and a method for fabricating the same, and in particular such that being preferably applicable to those having a charge storage film for storing electric charge.

3 ·

#### [0002]

### [CONVENTIONAL ART]

Any semiconductor memory device storing data by storing electric charge has a charge storage film for storing the charge, and writes or erases data by varying threshold voltage ( $V_{th}$ ) of the memory cell transistor depending on the amount of charge stored in the charge storage film.

[0003]

The aforementioned writing or erasure of data in, for example, a SONOS (semiconductor/oxide film/nitride film/oxide film/semiconductor)-type semiconductor memory device is effected by generating a potential difference between a gate electrode (word line) of a selected memory cell and a semiconductor substrate (bit line), and then by injecting hot electrons into the charge storage film, or by injecting holes based on band-to-band tunneling.

[0004]

[Patent Document 1]

Translated National Publication of Patent Application No. Hei 8-507411

[0005]

[PROBLEMS WHICH THE INVENTION IS TO SETTLE]

Conventional fabrication of the semiconductor memory device has, however, been suffering from a problem that the charge storage film was likely to store unnecessary charge during various process steps

in the fabrication. This resulted in generation of error or variation of charge to be stored in the charge storage film when the semiconductor memory device is operated for writing or erasure, which undesirably varied the threshold voltage and prevented the device from being stably operated.

[0006]

The present invention is accomplished considering the aforementioned problem, and is to provide a semiconductor memory device and a method of fabricating the device, both of which being aimed at avoiding storing of unnecessary charge into the charge storage film, and thus stabilizing the threshold voltage.

[0007]

[MEANS FOR SOLVING THE PROBLEMS]

The present inventors reached the following aspects of the present invention after extensive investigations.

[0008]

One aspect of the present invention relates to a method of fabricating a semiconductor memory device which comprises the steps of forming a charge storage film for storing electric charge; and erasing electric charge stored in the charge storage film by subjecting the charge storage film to hydrogen plasma treatment after the formation thereof.

[0009]

Another aspect of the present invention relates to a method of fabricating a semiconductor memory device which comprises the steps of forming a charge storage film for storing electric charge; and erasing electric charge stored in the charge storage film by subjecting the charge storage film to hydrogen annealing after the formation thereof.

[0010]

Still another aspect of the present invention relates to a semiconductor memory device such that having a charge storage film for storing electric charge, and having, in addition to a first contact hole used for wiring connection, a second contact hole not used for wiring connection but used for facilitating diffusion of hydrogen radicals or hydrogen molecules into said charge storage film.

[0011]

[EMBODIMENT]

- Basic Concept of the Present Invention -

In the field of fabricating semiconductor memory devices, hydrogen plasma treatment is typically carried out after contact holes for establishing wiring contact are formed, in order to remove foreign matters such as carbon contained in a barrier layer, which are derived from TDMAT (Tetrakis dimethylamino titanium) used as a source gas for forming the barrier layer by the CVD process. Removal of such foreign matters can be

accomplished by hydrogen plasma treatment within 35 seconds or around.

[0012]

On the other hand, conventional fabrication of the semiconductor memory device has been suffering from a problem that, once the charge storage film for storing electric charge was formed, the film was likely to store unnecessary charge during various process steps thereafter in the fabrication, which resulted in error or variation in the threshold voltage. The storing of unnecessary charge into the charge storage film is, however, unavoidable in the fabrication process, and thus only possible way was to erase the unnecessary charge already being stored into the film. After thorough considerations for addressing the problem, the inventors present reached the present invention described below.

[0013]

The present invention is designed so as to form the charge storage film, subject the charge storage film to hydrogen plasma treatment for a predetermined duration of time, to thereby allow hydrogen radicals to diffuse into the film, with which the stored unnecessary charge (negative charge) is cancelled. Carrying-out of the hydrogen plasma treatment after the contact holes are formed will be advantageous since the unnecessary charge in the charge storage film can be removed without causing any increase in the number of process steps.

### [0014]

The hydrogen plasma treatment for removing the unnecessary charge in the charge storage film is by no achievable by the aforementioned short-term means hydrogen plasma treatment for removing impurities such carbon, due to special feature of the process as whereby the stored unnecessary charge in the charge storage film must be erased. Our experimental results on the threshold voltage characteristics, which will be described later, revealed that the purpose of erasing the unnecessary charge in the charge storage film would never be achieved unless the hydrogen plasma treatment would be continued at least for 40 seconds, for the case where the erasure was to be effected through a titanium nitride film (CVD-TiN film) of 5 nm thick. We have, on the other hand, reached a conclusion that it was appropriate to finish the treatment within **9**0 seconds from the viewpoint of throughput in fabrication of the semiconductor memory device. Based on the discussion in the above, we concluded that a duration of time of 40 to 90 seconds was optimum for the hydrogen plasma treatment while taking both goals into account, that are, erasure of the unnecessary charge stored in the charge storage film, and assurance of a practical throughput in the fabrication process.

[0015]

As for a process in which the unnecessary charge stored in the charge storage film is erased by hydrogen

annealing in place of hydrogen plasma treatment, we concluded that an optimum duration of time is 30 to 90 minutes while taking both goals into account, that are, erasure of the unnecessary charge stored in the charge storage film, and assurance of a practical throughput in the fabrication process.

[0016]

As described in the above, the present invention is to provide a method capable of preventing the charge storage film from being stored with unnecessary charge, and of thus stabilizing the threshold voltage without causing any increase in the number of process steps in the fabrication, by making use of hydrogen plasma treatment (or hydrogen annealing) under well-adjusted conditions.

[0017]

- Specific Embodiments Applied with the Present Invention -

Next, specific embodiments of the present invention will be described referring to the attached drawings, which is an adaptation of the abovedescribed basic concepts on the semiconductor memory device and the method of fabricating the same. In the present embodiment, a buried-bit-line-type SONOS semiconductor memory device is disclosed as one example of the semiconductor memory device. Design of the semiconductor memory device employs planartype SONOS transistors in the memory cell area (core

area), and CMOS transistors in the peripheral circuit area.

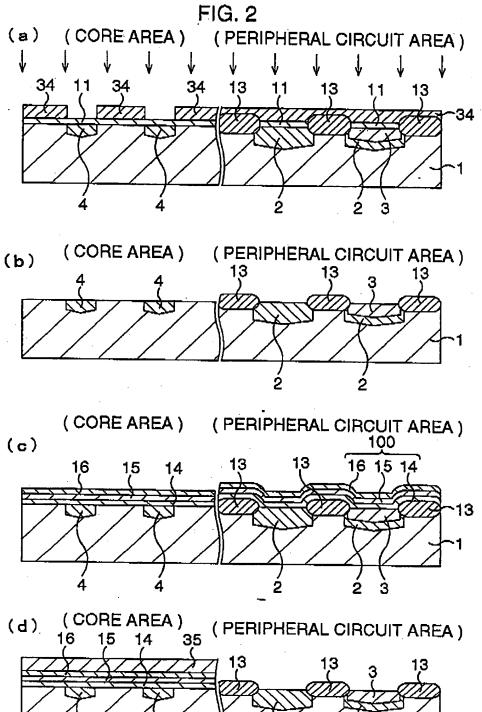

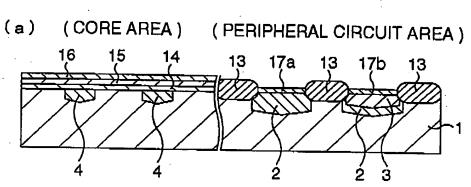

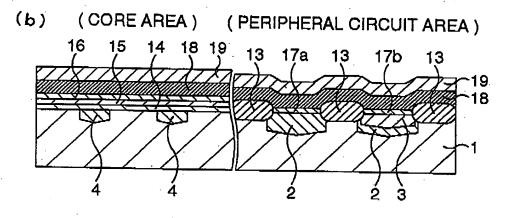

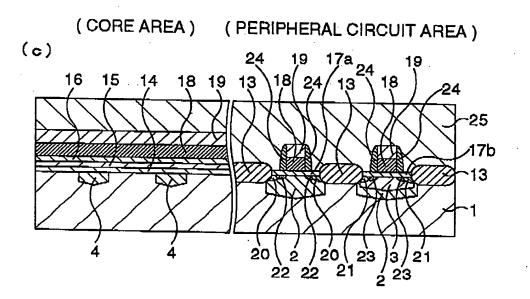

[0018]

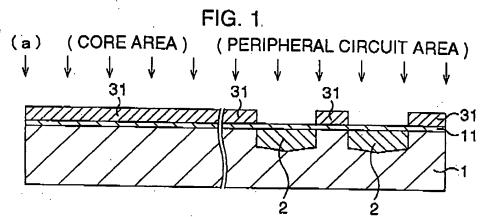

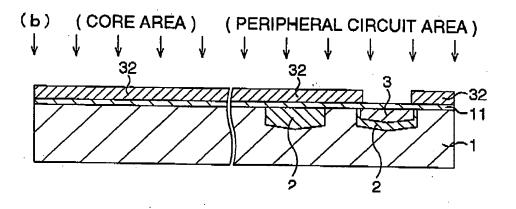

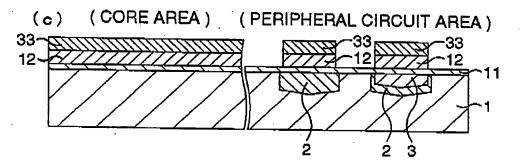

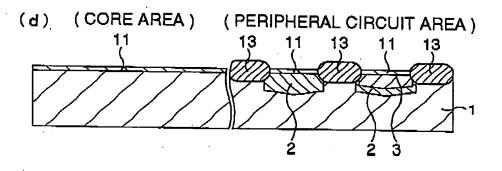

FIGS. 1(a) to 6(b) are schematic views sequentially showing process steps of a method of fabricating a semiconductor memory device containing the buried-bit-line-type SONOS transistors of the present embodiment. In FIGS. 1(a) to 3(c), the left halves show sectional views of the core area taken in parallel to a gate electrode (a word line), and right halves show those of the peripheral circuit area.

[0019]

First, as shown in FIG. 1(a), a semiconductor substrate 1 comprising a p-type silicon (Si) is thermally oxidized to thereby form a silicon oxide (SiO<sub>2</sub>) film **11** of approx. 20 nm thick. A resist pattern 31 is formed by photolithography so as to expose an area for forming transistors in the peripheral circuit area, phosphorus (P) ion is implanted over the entire surface, and the impurity is thermally diffused by annealing to thereby form an Nwell 2. The resist pattern 31 is then removed typically by ashing using  $O_2$  plasma.

[0020]

Next, as shown in FIG. 1(b), a resist pattern 32 is formed by photolithography so as to expose an area for forming an NMOS transistor in the peripheral circuit area, boron (B) ion is implanted over the entire surface, and the impurity is thermally

diffused by annealing to thereby form a P-well 3, where a triple-well structure is obtained in the NMOS transistor formable area. The resist pattern 32 is then removed typically by ashing using O<sub>2</sub> plasma.

[0021]

Next, a silicon nitride film 12 of approx. 100 nm thick is deposited on the silicon oxide film 11 by the CVD process. A resist pattern 33 is then formed by photolithography so as to be opened corresponding to areas where element isolation regions are to be formed, and the silicon nitride film 12 is dry-etched so as to be opened corresponding to areas where element isolation regions are to be formed, as shown in FIG. The resist pattern 33 is then removed typically 1(c). by ashing using O<sub>2</sub> plasma.

[0022]

Next, as shown in FIG. 1(d), a thick silicon oxide film 13 is formed by so-called LOCOS process only in the areas not covered with the silicon nitride film 12, to thereby partition the element active region. The silicon nitride film 12 is then removed by dry etching.

[0023]

Next, as shown in FIG. 2(a), a resist pattern 34 having a bit-line pattern is formed by photolithography, arsenic (As) ion is implanted over the entire surface under masking by the resist pattern 34, and the impurity is thermally diffused by annealing to thereby form a bit-line, impuritydiffused layer 4 which is used in common with source-

and-drain region, in the core area. The resist pattern 34 is then removed typically by ashing using  $O_2$  plasma.

[0024]

Next, as shown in FIG. 2(b), the silicon oxide film 11 is removed by wet etching using hydrofluoric acid (HF), to thereby expose the surface of the semiconductor substrate 1 in the core area and the element active regions in the peripheral circuit area.

[0025]

Next, as shown FIG. 2(c), a tunnel oxide film (silicon oxide film) 14 of approx. 7 nm thick is formed by thermal oxidation, a silicon nitride film 15 of approx. 10 nm thick is formed on the tunnel oxide film 14 by the CVD process, and a silicon oxide film 16 of approx. 7 nm thick is formed on the silicon nitride film 15 by the CVD process. This completes an ONO film 100 which comprises three films of the tunnel oxide film 14, silicon nitride film 15, and silicon oxide film 16. The silicon nitride film 15 herein functions as a charge storage film for storing electric charge in the semiconductor memory device.

[0026]

Next, as shown in FIG. 2(d), a resist pattern **35** is formed by photolithography so as to expose the peripheral circuit area, and the ONO film **100** in the peripheral circuit area is removed by dry etching. The

resist pattern 35 is then removed typically by ashing using  $O_2$  plasma.

[0027]

Next, the surface of the semiconductor substrate 1 is heated at a temperature as high as 1,000°C so as to form a silicon oxide film (SiO<sub>2</sub> film) of approx. 8 nm thick, as shown in FIG. 3(a). An unshown resist pattern is then formed so as to be opened in the area for forming a PMOS transistor in the peripheral circuit area, and the silicon oxide film in the PMOS transistor formable area i\$ removed by wet etching using hydrofluoric acid (HF). The unshown resist pattern is then removed typically by ashing using  $O_2$  plasma, and the surface of the semiconductor substrate 1 is again heated at a temperature as high as 1,000°C so as to form a silicon oxide film (SiO<sub>2</sub> film) of approx. 10 nm thick, to thereby form two different gate insulating films, that are, a gate insulating film 17a of approx. 10 nm thick in the PMOS transistor formable area and a gate insulating film 17b of approx. 13 nm thick in the NMOS transistor formable area.

[0028]

Next, as shown in FIG. 3(b), a polysilicon film 18 of approx. 100 nm thick is deposited by the CVD process in the core area and peripheral circuit area. Further on the polysilicon film 18, a tungsten silicide film 19 of approx. 150 nm thick is formed by the CVD process.

[0029]

Next, as shown in FIG. 3(c), the tungsten silicide film 19 and polysilicon film 18 are patterned by photolithography and succeeding dry etching, to thereby form gate electrodes comprising the tungsten silicide film 19 and polysilicon film 18 respectively in the core area, and in the PMOS transistor formable area and NMOS transistor formable area of the peripheral circuit area. The gate electrode herein in the core area is formed so as to cross with the bit-line, impurity-diffused layer 4 nearly at right angles.

[0030]

LDD-structured source-and-drain regions 20, 21 are then formed only in the peripheral circuit area.

More specifically, in the PMOS formable area, a ptype impurity ion is implanted into the surficial area of the semiconductor substrate 1 on both sides of the gate electrode, to thereby form an extension regions 22. On the other hand, in the NMOS formable area, an n-type impurity ion is implanted into the surficial area of the semiconductor substrate 1 on both sides of the gate electrode, to thereby form extension regions 23.

[0031]

Next, a silicon oxide film is deposited by the CVD process over the entire surface, and is then anisotropically etched (etch-back) from the top surface thereof so as to allow the silicon oxide film to remain

only on both side faces of the gate electrodes, to thereby form sidewalls 24.

[0032]

Next, in the PMOS transistor formable area, a pimpurity ion is type implanted into the surficial portion of the semiconductor substrate 1 on both sides of the gate electrode and sidewalls 24, to thereby form deep source-and-drain regions 20 which partially overlap the extension regions 22. On the other hand, in the NMOS transistor formable area, an n-type impurity ion is implanted into the surficial portion of the semiconductor substrate 1 on both sides of the gate electrode and sidewalls 24, to thereby form deep source-and-drain regions 21 which partially overlap the extension regions 23.

[0033]

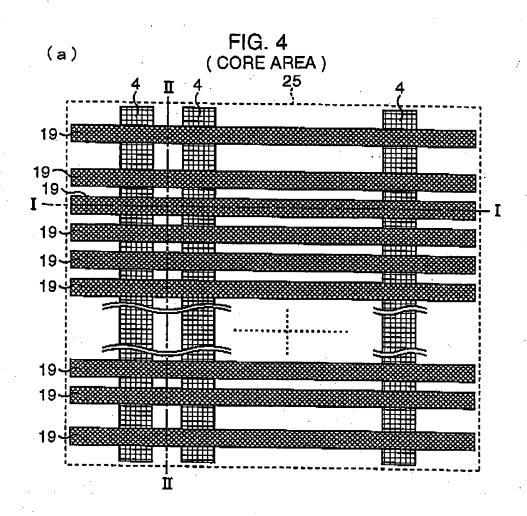

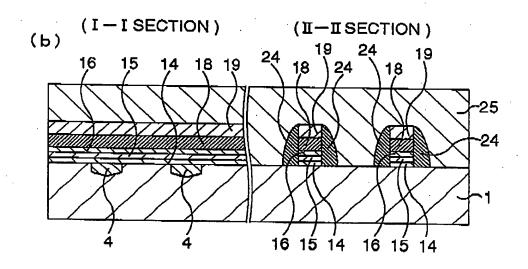

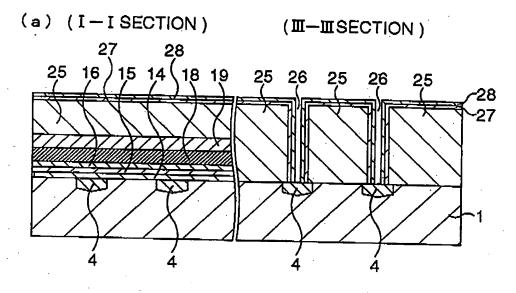

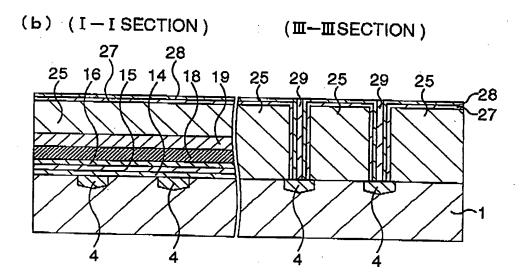

Thereafter, an insulating film 25, which.comprises a BPSG film or a silicon oxide film formed in a high density plasma, is deposited by the CVD process over the entire surface, and then planarized by the CMP (chemical-mechanical polishing) process. A schematic plan view of the core area is shown in FIG. 4(a), and a schematic sectional view taken along line I-I and line II-II in FIG. 4(a) is shown in FIG. 4(b).

[0034]

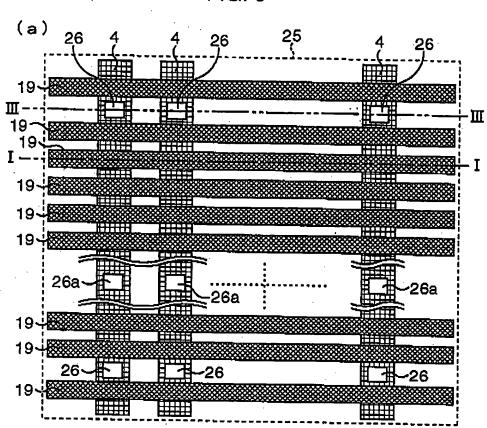

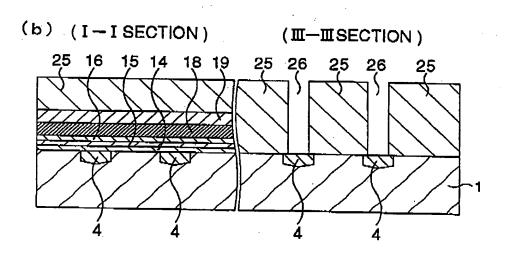

Next, as shown in FIGs. 5(a) and 5(b), contact holes **26** through which electrodes are drawn out are formed in the insulating film **25** by photolithography

and succeeding dry etching. A schematic plan view of the core area is shown in FIG. 5(a), and a schematic sectional view taken along line I-I and line III-III in FIG. 5(a) is shown in FIG. 5(b). As shown in FIG. 5(a), in the present embodiment, the contact holes 26 used for wiring connection are formed for every sixteen word lines 19 so as to reach the bit-line, impurity-diffused layers 4 at predetermined positions. There are also formed dummy contact holes 26a, which substantially do not contribute to wiring connection, so as to reach the bit-line, impurity-diffused layers 4.

[0035]

Next, the surface of the semiconductor substrate 1 cleaned by using a cleaning solution containing is hydrofluoric acid (HF) (hydrofluoric acid pretreatment) or by using plasma (plasma pre-treatment), and as shown in FIG. 6(a), a titanium (Ti) film 27, where Ti is a refractory metal, of approx. 5 to 80 nm thick is formed by the IMP (Ionized Metal Plasma) On the titanium film 27, a titanium nitride process. film 28 of approx. 5 to 50 nm thick is further formed by the CVD process using TDMAT as a source gas. FIG. 6(a) shows a sectional view taken along the line I-I and line III-III in the core area shown in FIG. 5(a).

[0036]

In the present embodiment, the titanium nitride film 28 is formed typically in a thickness of 5 nm by the CVD process, and is then subjected to hydrogen

plasma treatment at 350°C to 450°C for 40 seconds to 90 seconds. The titanium nitride film 28 herein is formed at a film forming temperature of 350°C to 450°C or around. It is also allowable to repeat, a plural number of times, the process steps of forming the titanium nitride film 28 in a thickness of 5 nm, and of subjecting the film to hydrogen plasma treatment for 70 seconds. Exemplary conditions for the hydrogen plasma treatment include hydrogen ( $H_2$ ) flow rate of 300 SCCM, nitrogen  $(N_2)$  flow rate of 200 SCCM, RF power of 750 W, and RF frequency of 350 kHz. Such hydrogen plasma treatment is successful in erasing unnecessary charge in the silicon nitride film 15 stored therein during the fabrication process. Raising the RF power to 850 W, for example, can raise the density of hydrogen radical and can successfully enhance effect of the erasure. In addition, if the hydrogen plasma treatment is carried out before the titanium nitride film 28 is formed, hydrogen radical can more effectively be diffused through the contact holes without being consumed in formation of methylamine (HNCH $_3$ ) or its analogue which otherwise possibly generates as a byproduct of titanium nitride when TDMAT is used as a source gas. Hydrogen plasma treatment before formation of the titanium nitride film 27 is also advantageous in allowing hydrogen to effectively diffuse through the contact holes without being gettered by titanium.

[0037]

For the case where the titanium nitride **28** is formed by the CVD process using TDMAT as a source gas, succeeding hydrogen plasma treatment for as long as 35 seconds or more can beneficially remove impurities such as carbon derived from TDMAT.

[0038]

It is also allowable to carry out the aforementioned hydrogen plasma treatment typically by the double-frequency process which is based on socalled ICP (induction-coupled plasma) process. The same effect can be obtained by hydrogen annealing, employed in place of hydrogen plasma treatment, at 400°C to 450°C or around for 30 minutes to 90 minutes or around.

[0039]

Next, a tungsten (W) film is deposited by the CVD process over the entire surface, and the tungsten film is planarized by the CMP process to thereby form tungsten plugs 29 as being buried in the contact holes 26 as shown in FIG. 6(b).

[0040]

hereafter, unshown various wirings including aluminum wiring are formed, and an unshown protective insulating film is formed as an uppermost layer. This completes a SONOS-type memory cell array in the core area, and CMOS-type transistors in the peripheral circuit area. The bit-line, impurity-diffused layers 4 in the core area herein are connected to the wirings.

On the other hand, the dummy contact holes **26a** shown in FIG. 5(a) are not used for the wiring connection even in the process of forming various wirings.

After the above-described process steps, the semiconductor memory device of the present embodiment is completed.

[0041]

While in the above-described embodiment, the hydrogen plasma treatment was carried out in succession to the formation of the titanium nitride film 28 by the CVD process, the present invention is by no means limited thereto, and any other process will be allowable provided that the silicon nitride film 15, which is a charge storage film, can be subjected to the hydrogen plasma treatment after the formation thereof. For example, the hydrogen plasma treatment can be effected at the time of the foregoing plasma pretreatment after the formation of the contact holes 26, or can be effected after the formation of the titanium film 27.

[0042]

While the LOCOS process was employed in the element isolation in the above-described embodiment, it is achievable by the STI (shallow trench isolation) process. It is also allowable to form the gate electrode by the SALICIDE process using a cobalt film, although the gate electrode in the above embodiment was formed by stacking the tungsten silicide layer on the polysilicon layer. While the core area of the SONOS-structured semiconductor memory device employed the planar constitution in the above, it may also have a constitution based on socalled, bit-line oxidation system. The semiconductor substrate may be of n-type, and the crystal orientation thereof may be (100) or (111). The wiring connection to the bit lines may be established in any number of lines, such as one for every eight word lines, one for every thirty-two word lines, or one for every twenty word lines. While the memory cell array in the core area in the above embodiment was of virtual grounding type, any other structures including NOR type and NAND type are allowable.

[0043]

The above embodiment is designed so that the silicon nitride film 15, which is a charge storage film, is subjected to the hydrogen plasma treatment after the formation thereof so as to remove electric charge stored therein, which therefore makes it possible to effectively erase unnecessary charge in the silicon nitride film 15 stored during the fabrication process of the semiconductor memory device. This successfully stabilizes the threshold voltage (Vth) of the semiconductor memory device. Carrying-out of the hydrogen plasma treatment within 90 seconds is beneficial in ensuring throughput in the fabrication.

[0044]

The above process also employs the dummy contact holes 26a which have substantially no contribution to the wiring connection, in addition to the contact holes through which the wiring connection is 26 to be established. successfully allows hydrogen This radicals (H<sup>\*</sup>) generated in the hydrogen plasma treatment or hydrogen molecules  $(H_2)$  in the atmosphere hydrogen annealing to diffuse of the into the semiconductor substrate not only through the contact holes 26 but also through the dummy contact holes 26a, which results in more effective erasure of the unnecessary charge stored in the silicon nitride film 15.

[0045]

- Characteristics Confirmation of Semiconductor Memory Device -

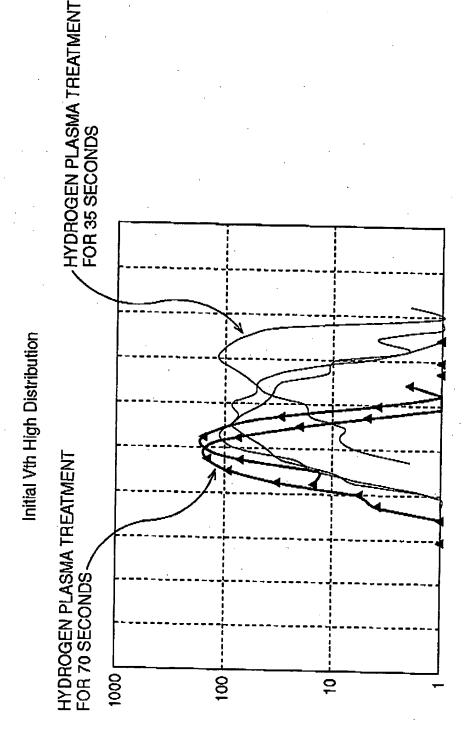

FIG. 7 is a schematic diagram of initial characteristics of the threshold voltage  $(V_{th})$  of the SONOS-type transistor according to the present embodiment.

Based on the definition in the above embodiment that the duration of time of the hydrogen plasma treatment after the formation of the charge storage film 15 should fall within a range from 40 to 90 seconds, this diagram exemplifies an experimental case in which the hydrogen plasma treatment was effected for 70 seconds, and a comparative case in which the hydrogen plasma treatment was effected only for 35 seconds.

[0046]

In FIG. 7, the abscissa represents relative value of the voltage threshold (V) of the measured semiconductor memory devices, the ordinate represents the number of measured semiconductor memory devices (frequency), the thick lines represent characteristic curves of the semiconductor memory devices subjected to 70 seconds of the hydrogen plasma treatment, and thin lines represent those of the semiconductor memory devices subjected to 35 seconds of the treatment.

[0047]

It is known from the diagram that the semiconductor memory devices subjected to 70 seconds of the hydrogen plasma treatment show lower threshold voltages with less variations therein. This is because the unnecessary negative charge stored in the charge storage film 15 was effectively erased by such 70 seconds of the hydrogen plasma treatment, which resulted in such lower threshold voltages with less variations,

[0048]

On the other hand, the semiconductor memory devices subjected to only 35 seconds of the hydrogen plasma treatment show higher threshold voltages with larger variations therein. This is because the unnecessary negative charge stored in the charge storage film 15 was not sufficiently erased by such 35 seconds the hydrogen plasma treatment, which of

resulted in such higher threshold voltages with larger variations.

[0049]

The results shown in FIG. 7 proved that the hydrogen plasma treatment effected for a predetermined duration of time (40 seconds or longer) can provide a semiconductor memory device having a stabilized threshold voltage and an excellent reliability.

[0050]

Various forms of the present invention are described below as appendix.

[0051]

[Appendix 1]A method of fabricating a semiconductor memory device comprising the steps of:

forming a charge storage film for storing electric charge; and

erasing electric charge stored in said charge storage film by subjecting said charge storage film to hydrogen plasma treatment after the formation thereof.

[0052]

[Appendix 2]The method of fabricating a semiconductor memory device according to appendix 1, wherein said plasma treatment is carried out over a duration of time of 40 seconds to 90 seconds.

[0053]

[Appendix 3]The method of fabricating a semiconductor memory device according to appendixes 1 or 2, further comprising, after the formation of said

charge storage film, a step of forming a contact hole through which a wiring connection is to be established, and then subjecting said film to said hydrogen plasma treatment through said contact hole.

[0054]

[Appendix 4] The method of fabricating a semiconductor memory device according to appendix 3, wherein said plasma treatment is carried out before, during, or after a barrier metal is formed along the inner wall of said contact hole.

[0055]

[Appendix 5]The method of fabricating a semiconductor memory device according to appendix 4, wherein said barrier metal has a thickness of 5 nm or less.

[0056]

[Appendix 6]The method of fabricating a semiconductor memory device according to any one of appendixes 1 to 5, wherein said plasma treatment is carried out at 350°C to 450°C.

[0057]

[Appendix 7]A method of fabricating semiconductor memory device comprising the steps of:

a

forming a charge storage film for storing electric charge; and

erasing electric charge stored in said charge storage film by subjecting said charge storage film to hydrogen annealing after the formation thereof.

[0058]

[Appendix 8]The method of fabricating a semiconductor memory device according to appendix 7, wherein said annealing is carried out over a duration of time of 30 minutes to 90 minutes.

[0059]

[Appendix 9]The method of fabricating а semiconductor memory device according to appendixes 7 or 8, further comprising, after the formation of said charge storage film, a step of forming a contact hole through which a wiring connection is to be established, and then subjecting said film to said hydrogen annealing through said contact hole.

[0060]

[Appendix 10] The method of fabricating a semiconductor memory device according to any one of appendixes 7 to 9, wherein said annealing is carried out at 400°C or above.

[0061]

[Appendix 11]The method of fabricating a semiconductor memory device according to any one of appendixes 1 to 10, wherein said charge storage film is any one of a nitride film, a double-layered film comprising an oxide film and a nitride film, and a three-layered film comprising an oxide film, a nitride film and an oxide film.

[0062]

[Appendix 12]A semiconductor memory device having a charge storage film for storing electric charge, said semiconductor memory device comprising:

first contact hole used for wiring connection, and;

second contact hole not used for wiring connection but used for facilitating diffusion of hydrogen radicals or hydrogen molecules into said charge storage film.

[0063]

[Appendix 13] The semiconductor memory device according to appendix 12, wherein said charge storage film is any one of a nitride film, a double-layered film comprising an oxide film and a nitride film, and a three-layered film comprising an oxide film, a nitride film and an oxide film.

[0064]

[EFFECT]

This present invention stabilizes the threshold voltage  $(V_{th})$  of the semiconductor memory device and provide a high trusty semiconductor memory device.

[BRIEF DESCRIPTION OF THE DRAWINGS]

[FIG. 1]

Schematic sectional views sequentially showing process steps of a method of fabricating a SONOS-type semiconductor memory device according to an embodiment of the present invention.

[FIG. 2]

Schematic sectional views sequentially showing process steps as continued from FIG. 1.

[FIG. 3]

Schematic sectional views sequentially showing process steps as continued from FIG. 2.

[FIG. 4]

Schematic views of a core portion of the SONOStype semiconductor memory device, previously shown in FIG. 3(c), according to an embodiment of the present invention.

[FIG. 5]

Schematic views of the core portion of the SONOStype semiconductor memory device obtained by the method of fabricating the SONOS-type semiconductor memory device in the embodiment of the present invention, as continued from FIG 4.

[FIG. 6]

Schematic sectional views sequentially showing process steps of the method of fabricating the SONOStype semiconductor memory device according to the embodiment of the present invention, as continued from FIG 5.

[FIG. 7]

A schematic diagram of the threshold voltage  $(V_{th})$  of the SONOS transistor.

[EXPLANETION OF CODES]

semiconductor substrate

2 N-well

3 P-well

4 bit-line, impurity-diffused layer

11 silicon oxide film

12 silicon nitride film

13 thick silicon oxide film

14 tunnel oxide film

15 silicon nitride film(charge storage film)

16 silicon oxide film

17a, 17b gate insulating film

18 polysilicon film

19 tungsten silicide film(word line)

20, 21 source-and-drain

21, 23 extension regions

24 sidewalls

25 insulating film

26 contact holes

26a dummy contact holes

27 titanium film

28 titanium nitride film

29 tungsten plugs

31-35 resist pattern

100 ONO film

[NAME OF DOCUMENT] ABSTRACT [SUMMARY]

[PROBLEM TO BE SOLVED] To provide a semiconductor memory device and a method of fabricating the device, both of which being aimed at avoiding storing of unnecessary charge into the charge storage film, and thus stabilizing the threshold voltage.

[SOLUTION] A silicon nitride film 15 for storing electric charge is formed on a semiconductor substrate 1 while placing a tunnel oxide film 14 in between, and the silicon nitride film 15 is then subjected to hydrogen plasma treatment so as to effectively erase unnecessary charge stored therein during various process steps in fabrication of the semiconductor memory device, to thereby stabilize the threshold voltage ( $V_{th}$ ) of the semiconductor memory device. [SELECTED DRAWING] Fig. 5

7-1

NUMBER OF MEASURED SEMICONDUCTOR MEMORY DEVICES(FREQUENCY)

a.r.b(v)

# This Page is Inserted by IFW Indexing and Scanning Operations and is not part of the Official Record

## **BEST AVAILABLE IMAGES**

Defective images within this document are accurate representations of the original documents submitted by the applicant.

Defects in the images include but are not limited to the items checked:

**BLACK BORDERS**

□ IMAGE CUT OFF AT TOP, BOTTOM OR SIDES

**FADED TEXT OR DRAWING**

**BLURRED OR ILLEGIBLE TEXT OR DRAWING**

SKEWED/SLANTED IMAGES

**COLOR OR BLACK AND WHITE PHOTOGRAPHS**

**GRAY SCALE DOCUMENTS**

□ LINES OR MARKS ON ORIGINAL DOCUMENT

□ REFERENCE(S) OR EXHIBIT(S) SUBMITTED ARE POOR QUALITY

• OTHER: \_\_\_\_\_

## IMAGES ARE BEST AVAILABLE COPY.

As rescanning these documents will not correct the image problems checked, please do not report these problems to the IFW Image Problem Mailbox.